碳化硅mosfet与硅mosfet相比,结构上有何区别?这种结构上的区别会造成性能上的哪些区别?

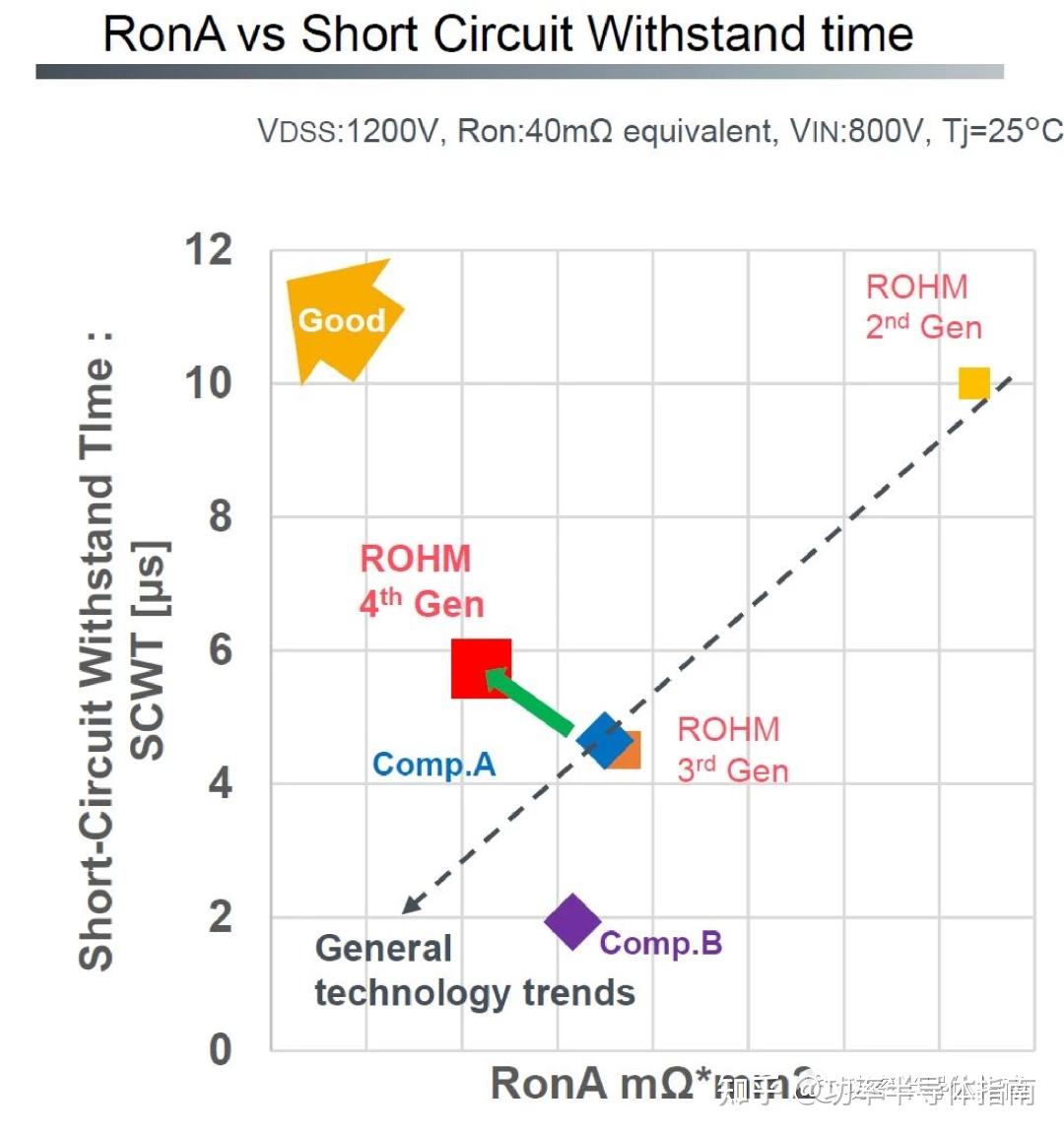

“ 罗姆(ROHM) 今年发布了他们的第 4 代 (Gen 4) SiC MOSFET 产品。声称“通过进一步改进原始的双沟槽结构,在不牺牲短路耐受时间的情况下,将单位面积的导通电阻比传统产品降低 40%,此外,与上一代 SiC MOSFET 相比显著降低了寄生电容,从而使得开关损耗降低了 50%”。 ”

罗姆(ROHM) 今年发布了他们的第 4 代 (Gen 4) SiC MOSFET 产品。新系列包括额定电压为 750 V(从 650 V 提升而来)和 1200 V 的 MOSFET,以及 56A/24mΩ 条件下的车规级TO247 封装组件。这一阵容表明罗姆将继续瞄准他们之前取得成功的车载充电器市场。

在他们的发布声明中,罗姆声称他们的第 4 代产品“通过进一步改进原始的双沟槽结构,在不牺牲短路耐受时间的情况下,将单位面积的导通电阻比传统产品降低 40%”。他们继续说道:“此外,与我们的上一代 SiC MOSFET 相比显著降低了寄生电容,从而使得开关损耗降低了 50%”。

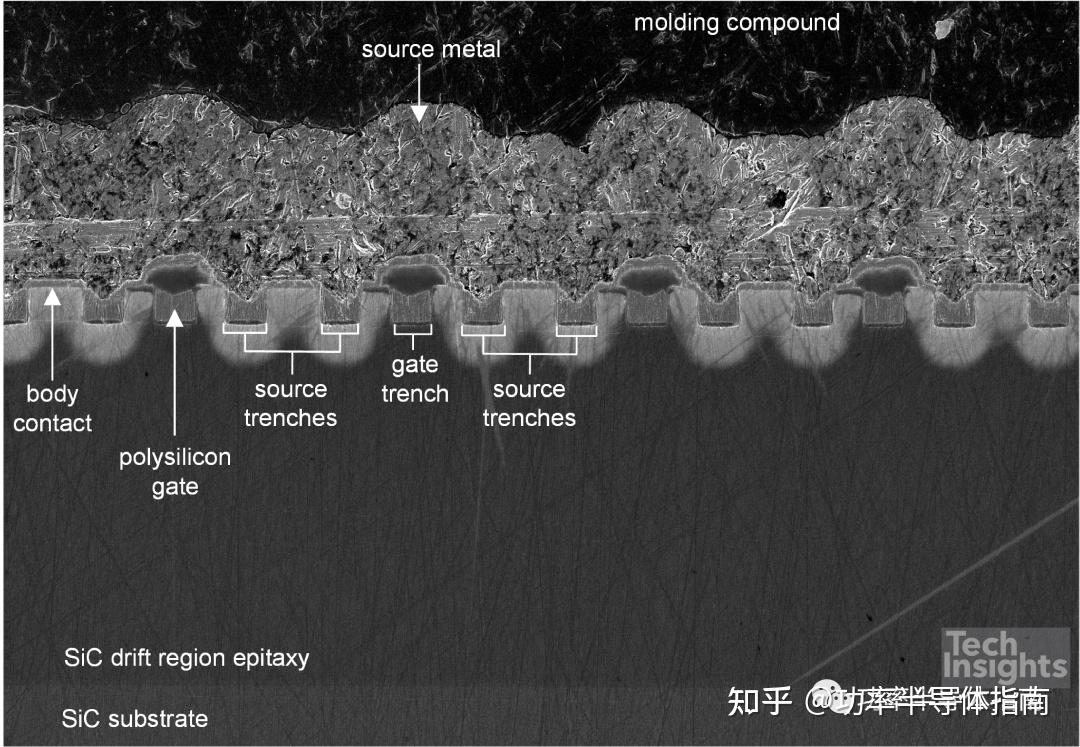

在几周内,TechInsights 迅速采购并剖析了新的 ROHM 第 4 代 MOSFET,并于 2022 年 7 月发布了第一批图片。从那时起,PGC 一直致力于提供这些器件的电气数据,这些数据结合截面图有助于我们解读罗姆在沟槽技术方面取得的进步。随着时间的推移,TechInsights 订阅者将获得全面的分析、测试设备的稳健性、可靠性和超出数据表的特性。同时,在本文中,我们将公开一些具有启发性的早期分析,以帮助我们验证上述罗姆的主张并了解他们所做的改进。

沟槽 MOSFET 基础知识

在 SiC 沟槽侧壁上制造的栅极具有更高的沟道迁移率,这意味着与平面器件相比,电子通过沟槽栅极的阻碍更少,这降低了通道电阻

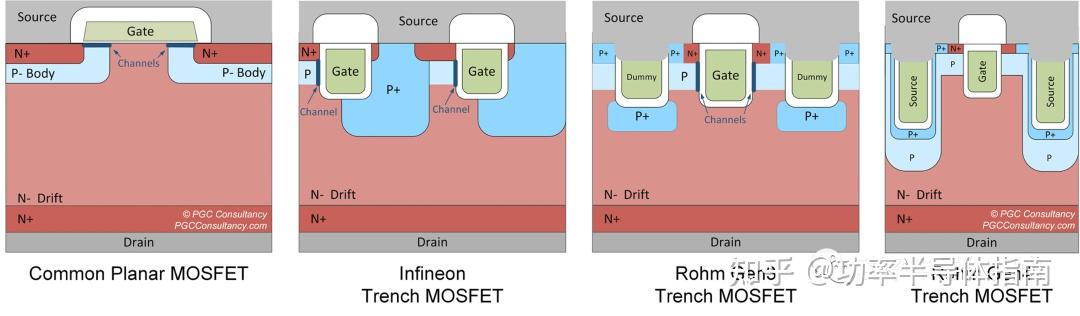

传统的“平面”MOSFET 的栅极和沟道区域位于半导体表面。平面 MOSFET 易于制造且相当可靠。然而,在减小芯片尺寸并因此提高良率的驱动下中,其横向拓扑限制了芯片最终可以缩小的程度。

沟槽 MOSFET 包括形成在沟槽边缘的栅极,该栅极已被蚀刻进 SiC器件。沟槽栅极用于设计较低电阻的器件—准确地说是较低的特定导通电阻Ronsp(单位:电阻 x 面积)。实现更低的 Ronsp(例如 15 mOhm)允许芯片制造商缩小芯片尺寸,使用更少的 SiC 材料,从而提高良率。

沟槽 MOSFET 较低的 Ronsp 背后有多种原因。首先,在 SiC 沟槽侧壁上制造的栅极具有更高的沟道迁移率,这意味着与平面器件相比,电子通过沟槽栅极的阻碍更少,这降低了通道电阻。其次,沟槽 MOSFET 可能会消除平面 MOSFET 的 JFET 电阻,在该区域中,来自两个通道的电流被挤压到 p 体接触之间的狭窄通道中。然而,正如我们下文将看到的,实用、务实的设计可能会导致重新引入类似 JFET 的区域。第三,与平面栅极的数量相比,垂直沟槽栅极的密度应该更大,因此可以减小单元间距并增加电流密度。

但是,沟槽 MOSFET 可能难以优化以实现可靠、稳健的运行。成功的设计必须解决在 SiC 器件顶部的峰值电场(比 Si 大 9 倍)的问题,同时保护同样位于器件顶部的精细栅极氧化物免受同一电场的影响。这种平衡行为需要巧妙但复杂的器件布局,否则漂移区将需要严重降额,从而侵蚀沟槽架构的增益。因此,沟槽 MOSFET 的一个缺点是它们的设计更复杂,通常需要更多的制造步骤,比如深高能注入(Infineon)或深沟槽蚀刻(ROHM Gen4),极大地增加了复杂性。

罗姆(ROHM)和英飞凌(Infineon)的沟槽设计

罗姆和英飞凌率先转向沟槽 MOSFET,但采用了截然不同的设计。ROHM 的 Gen 3 的横截面如下图 2 所示,以及图 1 中的卡通形式。ROHM 选择了更传统的设计,在每个栅极沟槽的每一侧边都有通道,每侧利用源级/虚拟沟槽,同时深 P 注入保护栅极沟槽。英飞凌让每条沟槽都发挥作用,每个沟槽的一侧都有一个通道,另一侧被深 P+ 注入所覆盖,该注入可保持来自栅极氧化物的高电场。这种布局可以让沟槽的沟道侧与 4° 离轴 SiC 晶体完美对齐,这是一种降低电阻的巧妙技巧。

图 2 中值得注意的是每个有源栅极沟槽之间的两个源极沟槽,与较宽的体电极一起,形成了很宽的沟槽器件的单元间距。然而,当从平面图中看到这个设备时,这种明显浪费的布局是有道理的。与传统的仅在一个维度上跨越器件的栅极不同,这款第 3 代器件的布局具有从上到下和从左到右运行的栅极,创建了一个巧妙的二维栅极网格,使每单位面积的栅极密度几乎翻倍。这在概念上类似于 Wolfspeed 的六边形布局,将栅极密度增加了大约 1.3 倍。然而,在 ROHM 最新的第 4 代发布之前,这两种沟槽器件都无法拥有低于同类最佳平面 MOSFET 的 Ronsp。第 3 代设计的另一个问题是,源极沟槽对存在非常高场强的栅极提供了多少保护?

罗姆(ROHM)第四代 SiC MOSFET

TechInsights 快速采购并剖析新的 ROHM 第 4 代 MOSFET,图 3 展示了新的第 4 代器件的高分辨率 SEM 图像。

与第 3 代器件相比,第 4 代器件有一些相似之处,也有一些显著的差异。相似的是 ROHM 采用传统沟槽 MOSFET 设计的方法,在栅极沟槽的两个侧壁上都有通道。然而,现在,每个栅极沟槽的两侧都有一个接地的源极沟槽,它延伸到漂移区的两倍深度。正如我们将要解释的,这是关键的设计特性,ROHM 巧妙地利用它来更好地保护栅极氧化物并降低电阻。每个栅极沟槽之间的单个虚拟/源极沟槽使得允许单元间距减少 3 倍。这标志着 ROHM 在第 3 代中使用的新型单元布局的终结,但是这几乎使栅极密度增加了一倍,有利于传统的一维条形版图。总之,这代表每单位面积的栅极沟槽密度净增加 50%(最小),这有助于进一步降低困扰其他器件的沟道电阻RCh,我们之前展示的 650 V 平面 SiC MOSFET 中该电阻可以贡献高达30%的总导通电阻(见 碳化硅(SiC)纵览—第 3 期:SiC MOSFET 的导通电阻)。与此同时,电阻的另一个主要贡献者衬底电阻Rsubs,也在这一代器件在第一次被减薄,大大减少了总导通电阻。

审查 ROHM 对其第四代 SiC MOSFET 的声明

使用 PGC 广泛的最先进的电气表征设备,并结合 Techinsights 的分析,已经审查了 ROHM 对这些器件的多项声明。我们直接对比了新的第 4 代沟槽型 750V MOSFET、第 3 代沟槽型 650V MOSFET 和一流的平面型 650V SiC MOSFET,它们都具有相似的导通电阻 Rds,on 值。首先是损耗。ROHM 在图4所示的第一个声明是,他们将导通损耗降低了 40%,从而实现了等效的芯片尺寸减小。事实上,通过 TechInsights 公布的横截面图,我们可以确认芯片有源区域的比导通电阻 (Ron × A) 几乎比上一代产品低 40%,尽管实际上器件的必要非有源区域略微降低了这一增益。进一步说明,新的 Ronsp 也比我们描述的一流的平面型器件小 20%。正如我们之前所讨论的,这是一个至关重要的进步,它可以缩小芯片尺寸,从而提高产量并降低成本 (见碳化硅(SiC)纵览—第 1 期:SiC 成本竞争力和降低成本的路线图简述)。

图中的第二个声明是,由于密勒电容的减小,开关损耗将降低。事实上,虽然我们比较的芯片的测试结果与之并不完全匹配,但我们可以确认 Crss 降低了约 90%(在额定电压下),并且 Coss 降低了一小部分,具体取决于电压。我们自己的开关基准测试正在进行中。

ROHM 提出的一项声明涉及从 650 V 到 750 V 范围内的额定电压增加。来自 ROHM:“750V 击穿电压确保设计裕度免受 VDS浪涌影响”。我们发现这是一个有趣的发展,整个行业都在发生这种发展。然而,实际上,在静态条件下测试的新型第 4 代器件的实际击穿电压如图 5 所示,约为 1000V,实际上低于在超过 1200V 时击穿的第 3 代器件。新的第 4 代器件与领先的平面型 SiC 器件不相上下。结合他们关于设计裕度的说法和实际数据,这非常令人印象深刻。他们正在允许他们的器件以 75% 的实际击穿电压使用,高于第 3 代的 50% 以上,这表明他们的可靠性要高得多。正如我们将在下一节中解释的那样,这种降额的减少是一个很大的改进,可以降低部分导通电阻 (见碳化硅(SiC)纵览—第 3 期:SiC MOSFET 的导通电阻)。在 PGC 实验室中对第 4 代器件进行短路测试很快就会进行,但 ROHM 的第三个有趣的说法是,尽管缩小了芯片尺寸并增加了电流密度,但它们的短路耐受时间却出乎意料地增加了。如果相信他们的话,这进一步证明了 ROHM 在其设备的可靠性和稳健性方面迈出了一大步。

总而言之,罗姆的第 4 代沟槽型 SiC 器件的强劲表现,有力回应了对早期 SiC 沟槽器件的许多批评。然而,我们想问的是这一切如何可能发生?

Rule 101:保护栅极氧化物

图 7 是 PGC 对新的第 4 代器件设计的图解复制。不按比例,图像强调了栅极周围的变化。关于 MOSFET 设计,特别是 SiC 沟槽 MOSFET 设计,主要是在器件处于关闭状态时保护栅极氧化物,阻止大电压。此时,器件表面存在高电场,如果允许该电场与栅极氧化物重合,则会导致栅极泄漏和可靠性问题。在第 3 代器件中,源极沟槽仅与栅极沟槽一样深,因此这些下方的 P+ 注入仅比栅极沟槽本身深一点。结果,图中所示的电场线(可以想象为正在膨胀的气球的外边缘)围绕沟槽角弯曲,并且可以更容易地与栅极沟槽的底部相互作用。

相反,ROHM 新的第 4 代器件的源极沟槽被注入到源极沟槽侧壁和底部的 P+ 区域包围,并且更深。这将保护栅极的 p-n 结向下推入漂移区,更远离它所保护的栅极氧化物。如第 4 代图所示,峰值场线(气球的外边缘)远离了栅极氧化物。

栅极保护的回报

栅极保护得更好,那又怎样?好吧,如果栅极没有得到很好的保护,例如在第 3 代器件中,则需要采取措施确保电场永远不会达到足以造成栅极损坏的峰值。因此,支持阻断电压的漂移区域被过度设计(降额 - 请参阅碳化硅(SiC)纵览—第 3 期:SiC MOSFET 的导通电阻)以支持远大于应用所需的额定电压。回想一下,用于 400V 电动汽车的额定 650V Gen 3 器件的实际击穿电压超过 1200V。虽然这确保了安全的长期运行,但代价是漂移区的导通电阻随着它可以支持的电压呈指数上升 (Rdr∝ V^2.28)。因此,通过更好地保护栅极,第 4 代器件只需要更少的降额。我们测量的击穿电压为 1000 V,相比第 3 代降低了 20% 以上,因此漂移区电阻可能降低了 40% 以上。这在 TechInsights 横截面中得到证实,新器件具有相似的漂移区宽度,尽管此外图 7 中所示的深沟槽也进一步有效地使其变薄。同时,我们还预计漂移区的掺杂将增加从而进一步降低电阻。

有效的栅极氧化物保护还可以有效提高可靠性。具体来说,这将解释为什么 ROHM 建议的栅极氧化物短路耐受时间已从最小值 4.5µs 增加到 5.5µs。在短路故障期间,支撑最高电场的器件区域通常会达到最高温度。如果那个位置离栅极更远,那么栅极烧坏的时间就会相应增加。

另一个巧妙的技巧:向超结 SiC 点头?

SiC 超结在学术界已经讨论了十年或更长时间,最近一次是由我的研究小组提出的。我们利用 7 µm 深的沟槽,并且在其侧壁上注入 p,提出了一种 1700V SiC 超结器件[1]。

ROHM 器件不是超结器件,它们的 p 型沟槽只是我们提出的那些器件的一小部分,但我们怀疑超结原理在源极沟槽下方的区域中起作用。毕竟,挤压在两个 P 柱之间的非常窄的 n 掺杂区域可能会显着增加器件的 JFET 电阻。然而,我们怀疑该区域的 n 型掺杂会高于漂移区,利用超结的电荷平衡原理(改天学习)在不破坏电场阻挡能力的情况下增加掺杂。

要点和结论

公平地说,我们对这种设计感到非常兴奋。它似乎是一种发挥 SiC 潜力的沟槽式 SiC 设计。我们从这个设计中得知,ROHM 找到了一种方法,使用他们的深沟槽设计来同时:

- 将单元间距减小三倍,大大降低了通道电阻。

- 保护栅极氧化层提供更高的可靠性,减少漂移区的降额,从而降低其电阻。

- 大幅降低了衬底电阻。

- 引入 JFET 区域(负面影响),但可能通过超结/电荷平衡原理降低其影响。

虽然目前只有英飞凌和罗姆的沟槽 SiC 器件可用,但博世也不甘落后,其他 IDM 可能会效仿,追逐潜在的良率和成本优势。进一步的证明将显示在采用率,我们是否会看到更多的电动汽车 OEM 和一级供应商在其车载充电器中采用该技术,甚至可能在以平面器件为主的传动系统逆变器中采用该技术。

参考文献:

[1] Baker, G. W. C., et al. "Optimization of 1700-V 4H-SiC Semi-Superjunction Schottky Rectifiers With Implanted P-Pillars for Practical Realization." IEEE Transactions on Electron Devices 69.4 (2022): 1924-1930.

版权声明:本文版权属于 PGC Consultancy和TechInsights,阅读原文请点击原文链接。中文版由 功率半导体指南 翻译完成,转载请注明出处。本公众号文章仅作学术交流,商业用途许可请联系著作权人。

原文链接

https://www.pgcconsultancy.com/post/rohm-gen-4-a-technical-review

Prof Gammon has 15 years of experience working in the design, fabrication and testing of silicon carbide power electronic devices. As well as being the founder of PGC, he is a Professor of Power Electronic Devices at the University of Warwick. He has led projects developing bespoke power devices (IGBTs, MOSFETs and diodes) rated from 1200 V up to 15 kV for Electric Vehicles, Space, Industrial Machines and the Grid. He has published over 80 papers, and 3 patents, with his work having been used across the SiC industry.

PGC Consultancy is a consultancy service provider dedicated to the rapidly expanding silicon carbide sector. As this leading wide bandgap material begins to threaten silicon’s dominance of the power electronics market, PGC can provide the specialist expertise your company will need in order to master this fast-evolving market. The team who founded PGC in 2020 have expertise from across the SiC value chain, in device design and fabrication, in SiC materials and epitaxy, in the testing and qualification of SiC products, and in the use of SiC products in applications such as the automotive industry. Please contact us to discuss your company’s needs. We can assist you with on-going consultancy, leading edge reporting, new IP generation, project management, and education.

TechInsights is widely recognized as the world’s leading provider of advanced technology analysis and intellectual property services, providing content and services to the world’s most successful technology companies. For over 30 years we have existed to support a fair marketplace where semiconductor and electronics intellectual property can be innovated and monetized. By revealing the innovation others cannot inside the broadest range of advanced technology products, we enable business leaders to make the best technology investment decisions and prove patent value with fact-based information.

Power Semiconductors Travelogue official account is dedicated to providing professional science popularization and industry analysis in the field of power semiconductors, including learning routes, key technical issues, industry development, and application prospects. It mainly covers wide-bandgap semiconductor materials silicon carbide (SiC) and gallium nitride (GaN), as well as ultra-wide-bandgap semiconductor materials gallium oxide (Ga2O3), diamond, et al. The editors of this official account are all postgraduate students from the University of Warwick, the University of Bristol, and the University of Electronic Science and Technology of China, et al. Contributions and academic exchanges are warmly welcome.

http://weixin.qq.com/r/nBzI0M7EOZNGrYqz90mO (二维码自动识别)

功率半导体指南 公众号致力于提供功率半导体领域的专业科普与产业分析,包括学习路线、关键技术问题、产业发展、和应用前景。主要涵盖宽禁带半导体材料碳化硅(SiC)和氮化镓(GaN),以及超宽禁带半导体材料氧化镓(Ga2O3),金刚石等等。

新公网安备 65010402001845号

新公网安备 65010402001845号